Исследователи разработали масштабируемый процессор аннелирования с 4096 спинами и параллельными возможностями для ускорения решения задач.

Процессоры аннелирования предназначены для решения комбинаторных задач оптимизации, где необходимо найти лучшее решение среди множества возможных вариантов. Эти процессоры находят практическое применение в логистике, распределении ресурсов и разработке лекарств и материалов. В контексте полупроводниковой технологии CMOS, компоненты процессоров аннелирования должны быть полностью «связаны». Однако сложность этих связей напрямую влияет на масштабируемость процессоров.

В новом исследовании, опубликованном в журнале IEEE Access под руководством профессора Такаюки Кавахары из Токийского университета наук, исследователи разработали и успешно протестировали масштабируемый процессор, который разделяет вычисления на несколько микросхем LSI. Эта инновация также была представлена на IEEE 22-м Всемирном симпозиуме по прикладному искусственному интеллекту и информатике (SAMI 2024) 25 января 2024 года.

Как объяснил профессор Кавахара, целью является выполнение сложной обработки данных непосредственно на периферии, а не в облаке. Используя уникальную архитектуру обработки, предложенную Токийским университетом наук в 2020 году, исследователи смогли создать полностью связанный процессор на одной микросхеме с использованием 28-нм технологии CMOS. Далее была разработана масштабируемая методика с параллельными микросхемами, эффективность которой была подтверждена с использованием программируемых логических матриц (FPGA) в 2022 году.

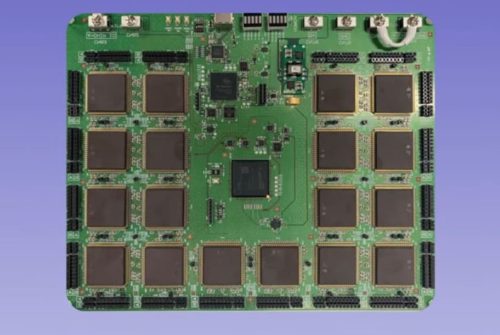

В ходе исследования, частично поддержанного грантом JSPS KAKENHI и Правительством Токио, команда создала масштабируемый процессор аннелирования, использующий 36 микросхем 22-нм CMOS и одну FPGA для управления. Эта технология позволяет создавать крупномасштабные системы на основе модели Изинга с 4096 спинами.

Процессор включает две ключевые технологии, разработанные в Токийском университете наук. Это «метод спиновой нити», который позволяет одновременно искать 8 решений, а также методика, сокращающая требуемое количество микросхем почти вдвое по сравнению с традиционными методами. Кроме того, процессор отличается низким энергопотреблением: он работает на частоте 10 МГц и потребляет всего 2,9 Вт (1,3 Вт на ядро). Это было подтверждено на практике с использованием задачи покрытия вершин с 4096 вершинами.

В плане отношения производительности к энергопотреблению процессор превзошел эмуляцию системы Изинга на компьютере (i7, 3.6 ГГц) в 2306 раз и превзошел центральный процессор и арифметический чип в 2186 раз.

Успешная проверка работоспособности процессора открывает возможности для увеличения его мощности. Профессор Кавахара поделился планами по развитию технологии в будущем, отметив, что команда планирует разработку системы с вычислительной мощностью, эквивалентной квантовому компьютеру 2050 года, без необходимости в системах охлаждения или облачных инфраструктурах, с использованием текущих полупроводниковых процессов. Цель — достичь 2 миллионов спинов к 2030 году и создать новые цифровые индустрии.